最多核的cpu

大家知道现在cpu最多有多少核吗?不知道的话跟着小编一起来了解一下最多核的cpu吧。

最多核的cpu介绍

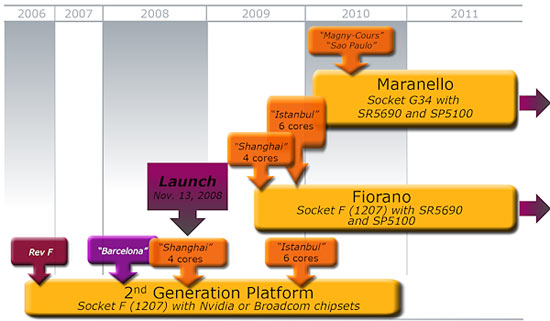

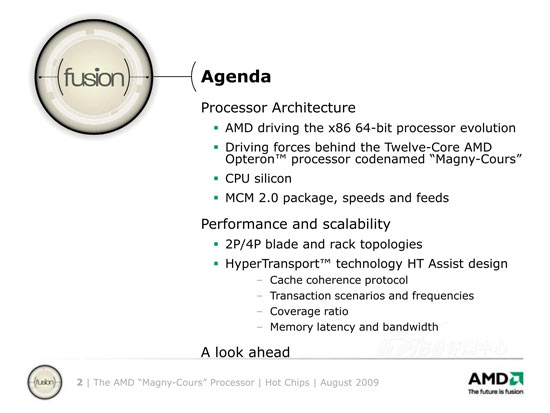

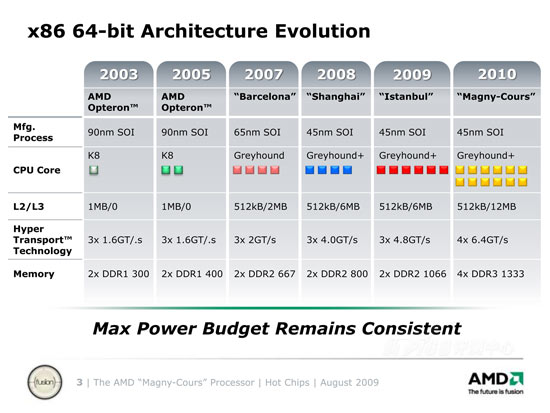

【IT168 服务器频道】早在2009年,在Istanbul刚发布不久的时候,AMD就在美国斯坦福大学举办的Hot Chip 21上发布了再下一代服务器平台的情况,这就是预计在2010年发布的12核心处理器:Magny-Cours,马尼库尔,这是首款具备了12个核心的x86处理器。直到今天为止,Intel的Nehalem处理器才步入8核心。

2010年3月30日:12核心即将到来

Magny-Cours:多种改进

Magny-Cours:45nm SOI、十二核心、4x 6.4GT/s总线、4x DDR3 1333内存

本质上来说,Magny-Cours其实是其上一代Istanbul的改进版本,采用的处理器微架构并没有大幅度的变化。AMD下一代的处理器微架构大约会在2011年登场,叫做Bulldozer(推土机)。那么,Magny-Cours是如何从Istanbul的六核心一跃达到十二个核心呢?

*关于Magny-Cours,我们已经有了不少资料,因此这里就说一些之前没说过或者说的不够清楚的地方

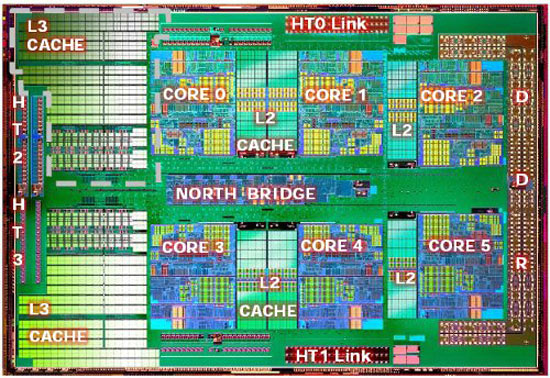

和Istanbul一样,Magny-Cours仍然是基于45nm SOI工艺,实际上,它就是将两个Istanbul封装在了一起,并做了一些改进,这个工艺就是业界常见得MCM(Multi Chip Module,多芯片模块)封装。

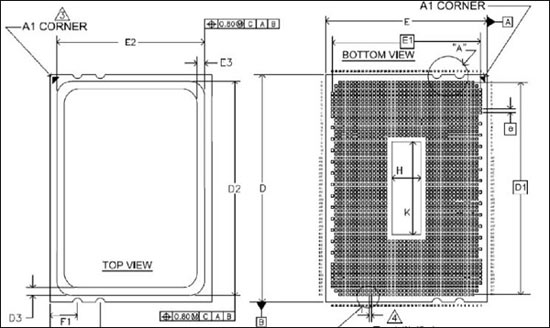

比原来显得更细长了,接口也从老的Socket F 1207变更为G34

Magny-Cours晶圆图

核心 方面也必须做出改变,为了核心能直接连接,要额外多设计些HT总线才成,因此,每一个Magny-Cours核心的HT总线从Istanbul的3条增加到了4条:

HT0、HT1、HT2、HT3,一共四条

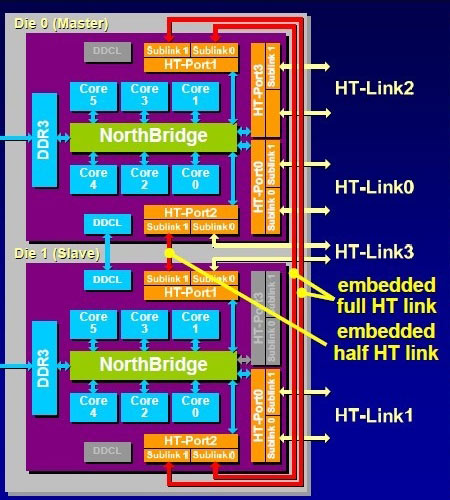

整个12核心CPU对外的HT总线条数也是4条,不过,和人们通常想的不太一样,Magny-Cours并不是使用了两个HT总线进行内部互联,它使用了1.5条HT总线。具体如下面两幅图所示:

内部架构图一(应该很接近或者就是真实情况)

官方给出的内部架构图(可见,P0是上一个图的Die 1,P1是上一个图的Die 0,刚好反过来)

笔者整理如下:

P0:5个HT链接,一个外部的x16 cHT和一个x8 cHT,还有一个x16弃而不用(NC:No Connection),一个内部的x16 cHT和一个x8 cHT连接到P1

P1:5个HT链接,和P0一样,只是P0弃而不用的x16 cHT现在引出

整个处理器内部:2个HT链接,其中一个x16 cHT链接,一个x8 cHT链接

整个处理器外部:5个HT链接,其中三个x16的全链接,一个由P0提供,两个由P1提供;最后是两个x8的半链接,每个核心模块提供一个

这样组装起来的话,Magny-Cours倒是提供了4个x16的cHT总线链接,不过其中一个是由两个核心模块提供的x8拼起来的。这就带来了疑问——cHT是什么?请看下一页。

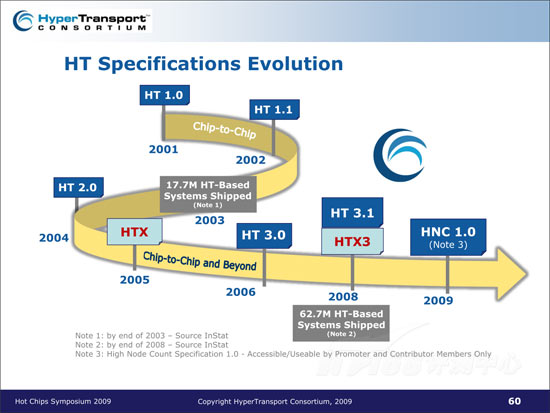

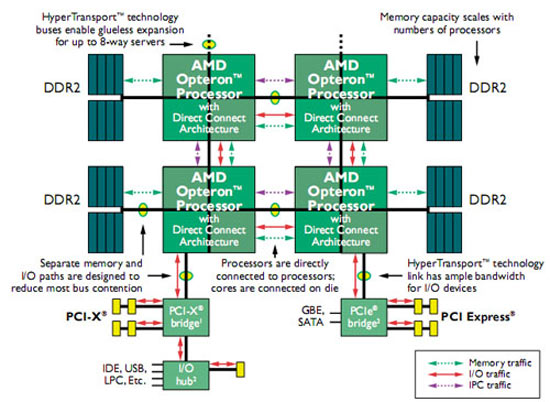

尽管在桌面市场上,HT 2.0、HT 3.0已经得到了广泛的应用,但是在服务器平台上,AMD为了延续Socket F(1207)平台以保护客户利益,因而没有做大规模升级。而随着马尼库尔的到来,AMD G34平台正式采用了新的HT总线,各种版本的HT总线性能对比如下所示,目前最新的版本是3.1:

HT总线之路

历代HT总线对比;Istanbul支持HT 3.0,但是由于平台的缘故通常达不到

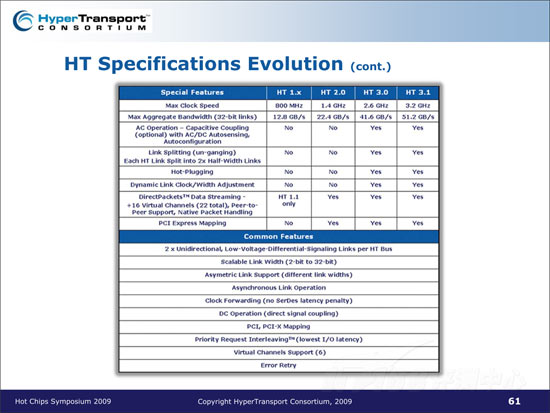

HT 3.1将时钟频率提升到了3.2GHz,而服务器平台之前的只有800MHz,带宽从12.8GB/s提升到了51.2GB/s,提升幅度达到了300%,跨度非常之大,预计对多路服务器性能的具有很大的正面作用。作为对比,竞争对手的单个QPI目前提供的是25.6GB/s的总带宽。除了巨大的带宽之外,HT 3.1还提供了一个Link Spliting(un-gangling)的技术,笔者将其翻译为链路分割(拆分)模式,它意味着每一个HT链接可以分割为两个半链接,只拥有一般的带宽但是具有完整的连接作用。HT 1.x和HT 2.x都没有这个功能。

HT链路分割技术可以用于构建大规模的的SMP系统

通过HT链路分割技术,Magny-Cours不仅实现了内部通过1.5个全链接互联的结构,还可以将4个外部全链接分割为8个半链接,从而形成一个8路96核心、包含8个I/O芯片的大型SMP系统,如上图所示。HT 3.1还提供了热插拔、AC/DC自动操作转换、动态链路时钟/位宽调整、DirectPackets数据流、PCI Express映射等增强功能,总的来说,进步非常大。

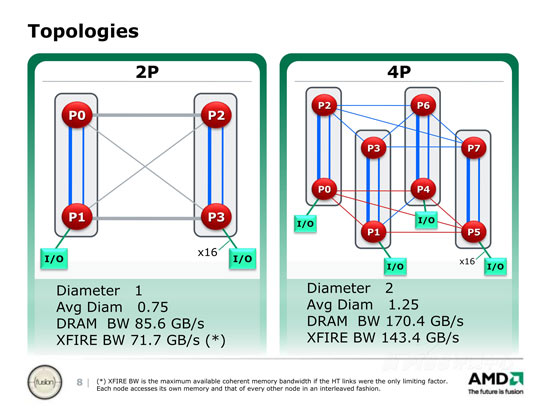

2路与4路Magny-Cours系统

4路Magny-Cours系统

最后,每一个Magny-Cours处理器可以支持达4通道的DDR3 1333内存,比起上一代的Istanbul(双通道800)也是一个不小的飞跃。

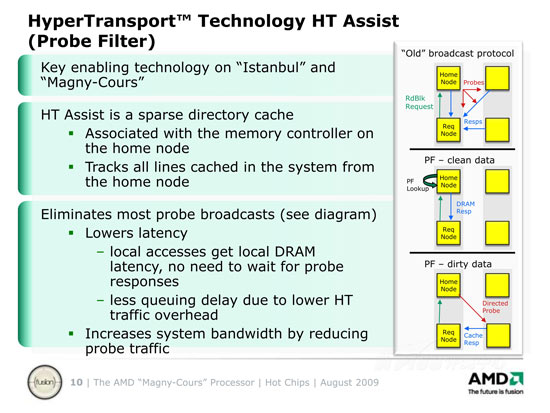

MCM多核心和HT 3.1总线是Magny-Cours的最大特点(内存系统从DDR2升级到DDR3也算一个),此外,Magny-Cours搭载的HT Assist技术也是一个比较重要的技术之一,这个技术在Istanbul上已经出现,但是它对于核心更多的Magny-Cours来显得更为重要。

Cache Coherence,缓存一致性;Cache Coherence NUMA(ccNUMA)是目前多路处理器系统的主流架构

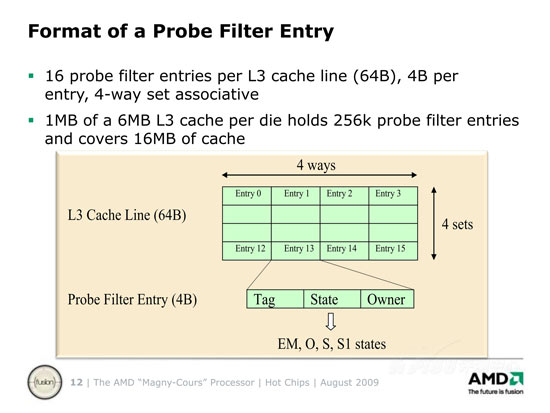

HT Assist就是Probe Filter,作用是用来提升多路处理器系统维持缓存一致性的效率,在前面我们提到的cHT,就是指缓存一致性的HT总线系统。HT Assist是用一个Probe Filter部件来侦测、缓存并加速HT总线上的缓存一致性操作:

HT Assist技术就是增加的Probe Filter部件

HT Assist实际上借用了L3缓存的一部分。在关闭HT Assist时,每个Magny-Cours可以获得12MB的L3缓存容量,而打开HT Assist之后,将会只剩下10MB的L3,以及2MB的HT Assist缓存容量,每个Die分别有5MB的L3和1MB的HT Assist缓存。

HT Assist工作原理

通过侦测本地缓存线上的操作,避免了原有情况下,一个CPU需要获得远端缓存页面需要进行广播并导致多个核心中断并响应的情况。在HT Assist下,只需要很少的操作就可以完成,并且不会打扰无关的处理器,节约了总线带宽。

1MB的HT Assist缓存可以覆盖16MB的L3缓存

最多核的c

最多核的cpu的评论条评论